Guia prático para construção de Flip-Flop com componentes discretos

https://www.lucasmantuan.com.br

https://github.com/lucasmantuan

https://www.linkedin.com/in/lucasmantuan

Introdução

A eletrônica digital e analógica pertencem ao mesmo universo, a eletrônica digital é apenas uma especialização da eletrônica analógica, sendo uma condição limitada desta. Embora sinais analógicos sejam, em essência, mais ricos em detalhes (já que, ao convertermos sinais analógicos em digitais, perdemos resolução), optamos pelo digital devido à simplicidade na comunicação, menor interferência, menos ruído e facilidade de armazenamento. O digital então é uma subdivisão prática e limitada do amplo universo da eletrônica analógica, definida pela utilização exclusiva de valores discretos.

Estes valores discretos são os níveis lógicos utilizados na comunicação digital, representados por 1 (nível de tensão alto, VCC) e 0 (nível de tensão baixo, GND). Apesar dessa definição clara, é importante ressaltar que, fisicamente, as tensões podem assumir qualquer valor entre VCC e GND, uma característica natural dos sinais analógicos. Mas, para facilitar o processamento, o armazenamento e a análise, convertemos essas grandezas contínuas em sinais digitais, justamente por suas vantagens, como imunidade a ruídos e a menor demanda de espaço para armazenamento dos dados.

Latch

O latch é o elemento mais simples de armazenamento de memória em circuitos digitais, responsável por guardar um único bit de informação. Trata-se de uma memória volátil, ou seja, os dados armazenados desaparecem em caso de falta de alimentação elétrica. O latch serve de base para a construção de todos os flip-flops e memórias digitais.

O circuito de um latch básico é formado por dois transistores, em que a base de cada um é conectada ao coletor do outro, formando uma realimentação responsável pela manutenção do estado interno (feedback). O sinal de entrada é aplicado na base, alterando o estado do circuito para armazenar o novo dado. Por isso, o latch também é conhecido como circuito biestável. Os resistores limitam as correntes nos terminais dos transistores, protegendo os componentes.

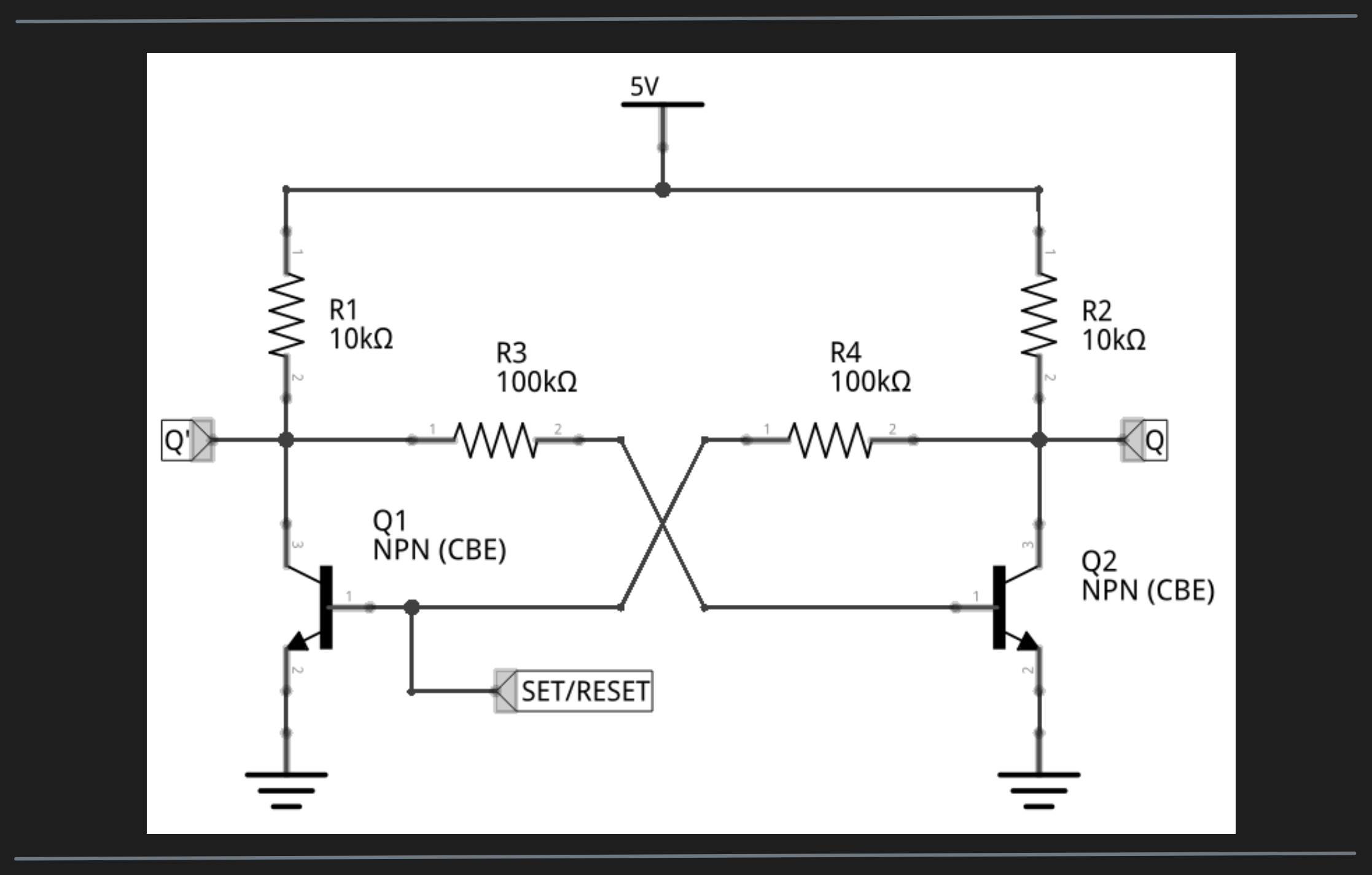

Esquemático

O circuito acima representa um latch prático implementado com transistores bipolares. Os coletores dos transistores estão ligados ao VCC por meio de resistores (R1 e R2). O funcionamento desse circuito baseia-se no controle do fluxo de corrente através de cada transistor, definindo claramente os níveis lógicos do latch.

Quando um dos transistores está em condução (ligado), ele cria um caminho de baixa resistência entre seu coletor e o terra (GND), fazendo com que a tensão em sua saída (Q ou Q') caia praticamente a zero, correspondendo ao nível lógico 0. Em contrapartida, quando o transistor está em corte (desligado), não há passagem de corrente do coletor para o emissor. Nesse caso, o resistor conectado ao coletor puxa a saída para o nível de tensão da alimentação positiva (VCC), resultando em um nível lógico 1.

Essa configuração lógica é mantida graças à realimentação cruzada (feedback), onde a base de cada transistor é alimentada pelo coletor do outro. Essa característica fundamental garante a estabilidade do circuito, mantendo o estado interno mesmo após a remoção do sinal de entrada, armazenando temporariamente um bit de informação. O estado só é alterado com a aplicação de um novo sinal na entrada em SET/RESET.

Os resistores de pull-up (R1 e R2) mantêm as saídas Q e Q' em nível alto (próximo a 5V) quando os respectivos transistores estão desligados. Em situação inicial (sem pulso aplicado), por exemplo, se o transistor Q2 está em corte, a corrente flui de VCC pelo resistor R1 até o nó Q', mantendo-o em nível alto. Ao dar um pulso em SET, o transistor Q1, conectado ao nó Q', entra em condução, criando um caminho direto entre Q' e o GND, desviando a corrente diretamente para o terra através do transistor ligado (Q1). Com isso, a tensão em Q' cai para praticamente 0V (nível lógico baixo). Ao aplicar o RESET, ocorre o inverso, invertendo os papéis dos transistores e das saídas (Q e Q').

A relação entre Q1 e Q2, pela realimentação cruzada, explica como o pulso em SET/RESET aplicado diretamente à base de Q1 afeta indiretamente Q2. Quando Q1 liga, força Q2 a desligar, e quando Q1 desliga, força Q2 a ligar. Essa interação é essencial para garantir o comportamento biestável do latch.

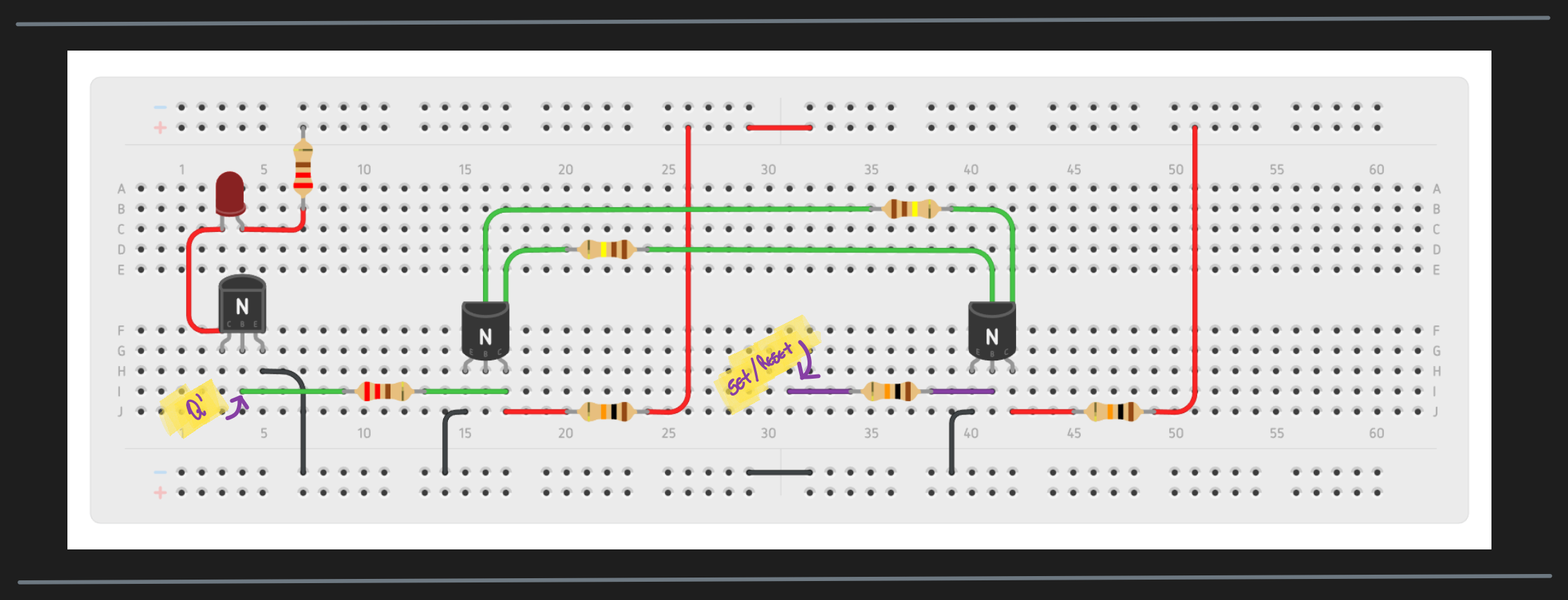

Protoboard

Tanto Q e Q' são saídas complementares do latch, correspondendo aos nós em que estão ligados os resistores de pull-up. Na protoboard, elas são os pontos onde se conectam indicadores ou circuitos externos. Em nosso exemplo, um terceiro transistor pode ser utilizado como driver de corrente para controlar um LED, evitando que a carga interfira no funcionamento interno do latch. Por exemplo, a saída Q', em nível alto por padrão, polariza a base do terceiro transistor, fazendo o LED acender. Ao aplicar o SET, o transistor Q1 conduz e leva Q' ao nível baixo, desligando o transistor driver e apagando o LED.

Portanto, quando se aplica um pulso SET:

- O Q vai ao nível alto (5V), acionando um LED conectado;

- O Q' vai ao nível baixo (0V), apagando o LED conectado.

Essa ação de puxar para o terra (baixo) caracteriza o funcionamento essencial do latch.

Tabela Verdade

Flip-Flop

O flip-flop é uma evolução do latch, com a adição de um circuito de clock. Ele é um elemento fundamental no armazenamento digital de 1 bit, presente em memórias, registradores e outros dispositivos digitais. No flip-flop, o dado só é armazenado ou atualizado na presença de um pulso de clock.

Armazenar ou atualizar um dado na presença de um pulso de clock significa, que o flip-flop só altera o valor armazenado quando recebe um sinal específico chamado clock, sendo diferente do latch, que pode mudar seu estado a qualquer momento em resposta à entrada. Ele é um sinal periódico, normalmente uma onda quadrada, utilizado para sincronizar as operações nos circuitos digitais. A cada pulso desse sinal, o flip-flop verifica a entrada e, conforme sua lógica de funcionamento, pode atualizar a saída.

A presença do pulso de clock atua como uma autorização para que o flip-flop processe e registre o novo dado, permitindo o controle preciso de quando as mudanças acontecem no circuito. Existem diferentes métodos de acionamento do clock, por nível (level triggering) ou por borda (edge triggering). A maioria dos circuitos digitais utiliza acionamento por borda, pois o dado é transferido apenas no momento da transição do sinal de clock.

No método de disparo por nível (level triggering), o flip-flop responde enquanto o sinal de clock permanece em um determinado nível lógico, seja alto (1) ou baixo (0). Nesse caso, enquanto o clock estiver mantido nesse nível, o flip-flop pode continuar processando mudanças na entrada.

Já no disparo por borda (edge triggering), o flip-flop responde apenas no instante em que ocorre uma transição do clock, seja na borda de subida (transição de 0 para 1) ou na borda de descida (transição de 1 para 0). Dessa forma, o dado só é transferido para a saída exatamente no momento dessa mudança, evitando que alterações indesejadas na entrada interfiram no valor armazenado durante o restante do ciclo do clock.

É por esse motivo, a maioria dos circuitos digitais utiliza o acionamento por borda, garantindo maior precisão e estabilidade no armazenamento das informações.

Diagrama Flip-Flop

D Flip-Flop

Em um D Flip-Flop (Data Flip-Flop), o valor aplicado à entrada DATA IN (D) representa o valor lógico que se deseja armazenar. Trata-se de um sinal digital que pode assumir nível alto (aproximadamente 5V) ou nível baixo (0V) em circuitos típicos alimentados por 5V. Esse sinal pode permanecer estático em um desses níveis até que ocorra uma transição de clock, momento em que o valor é efetivamente transferido para a saída.

O sinal de clock (CLK) também é um pulso digital variando entre 0V e 5V, porém sua função é de determinar o instante em que o valor presente em DATA IN será capturado e transferido para a saída. Essa captura ocorre apenas durante as transições do clock (normalmente na borda de subida), e não enquanto ele permanece estático. Portanto, enquanto DATA IN define o valor, CLK define o momento exato em que esse valor será armazenado.

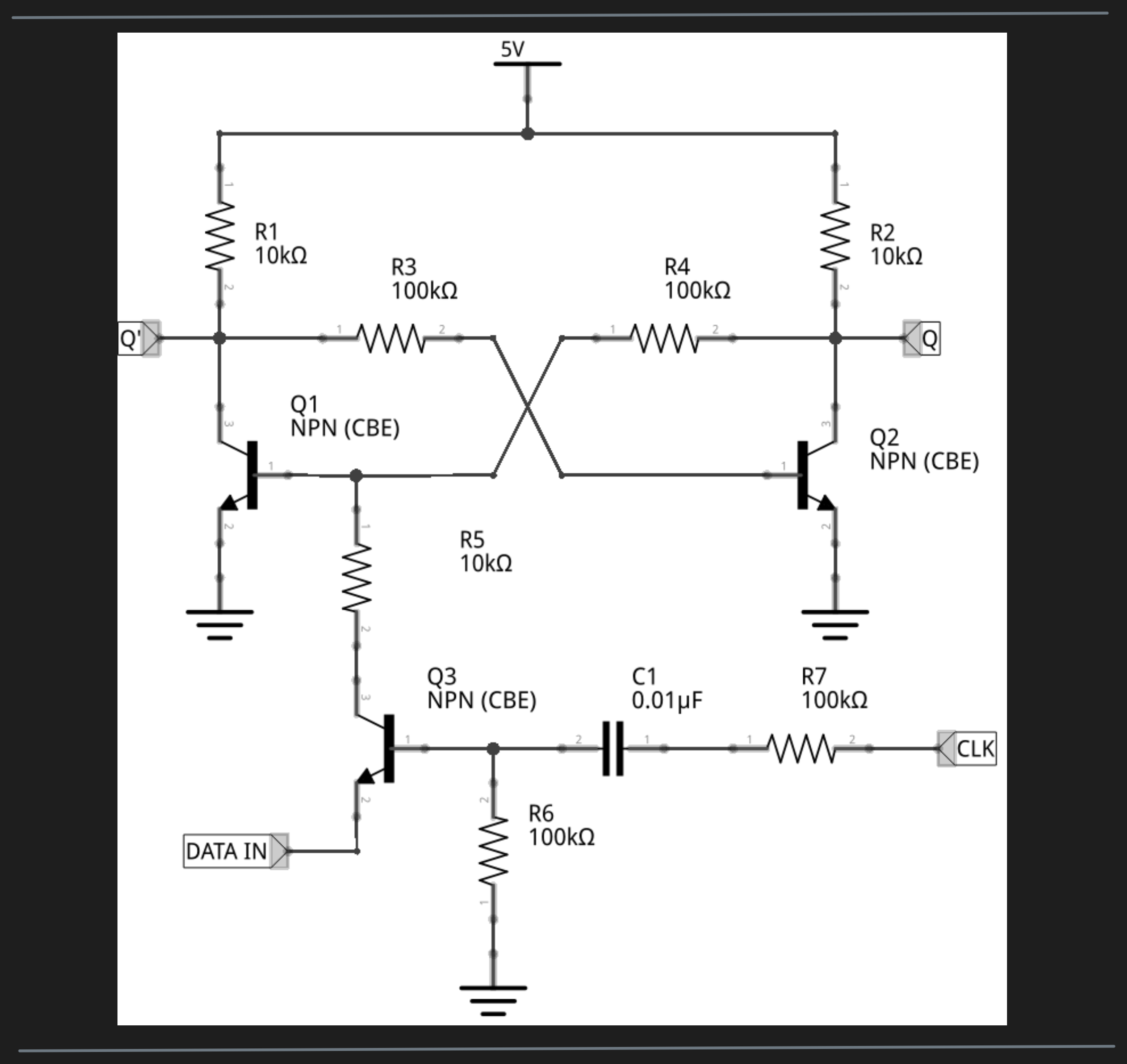

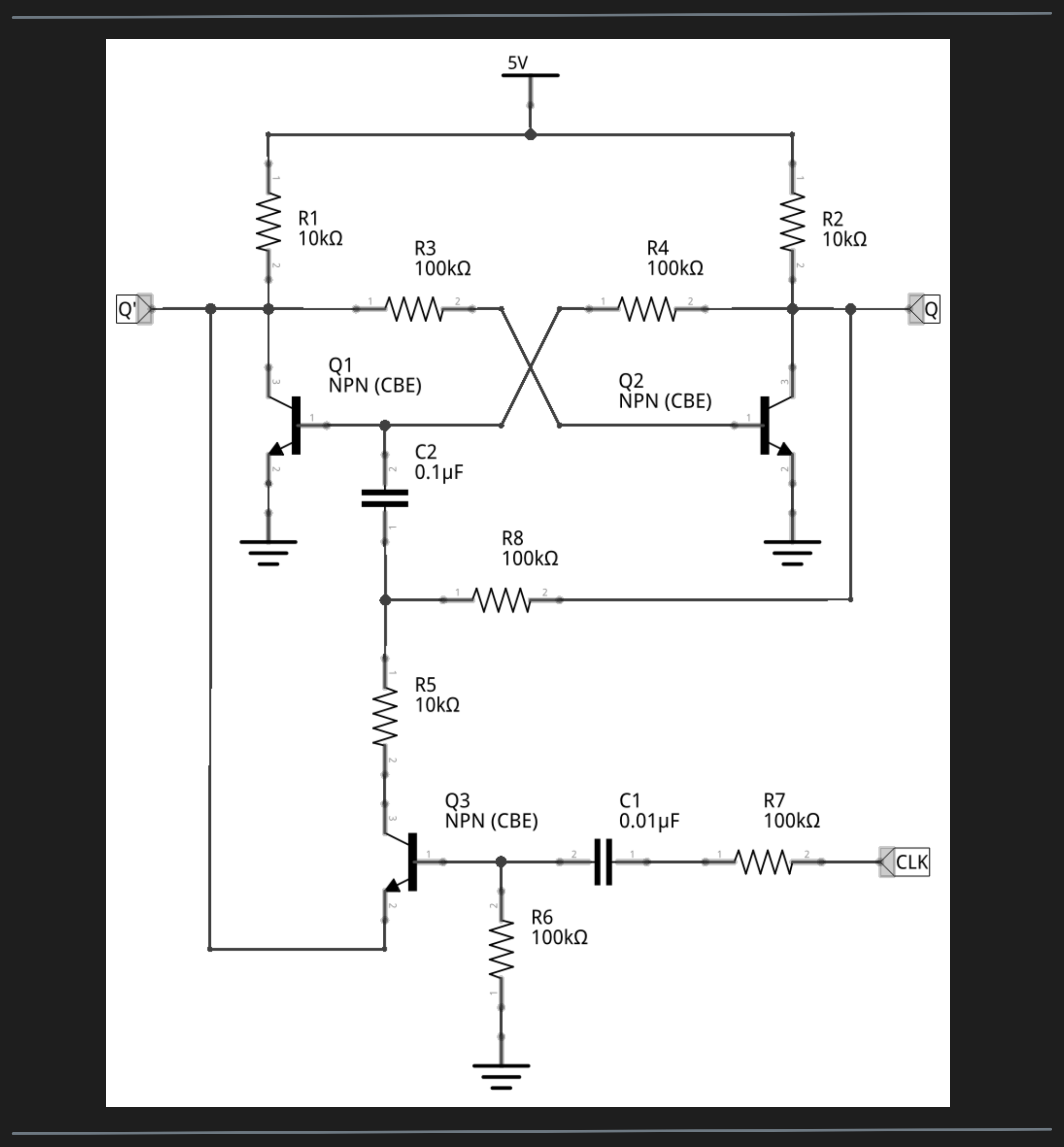

Esquemático

No funcionamento prático do D Flip-Flop, o valor aplicado à entrada D é copiado para a saída Q durante um pulso de clock. Se a entrada D estiver em 1, a saída Q torna-se 1, e sua saída complementar Q' assume o valor 0. Caso a entrada esteja em 0, a saída Q torna-se 0 e Q' passa a 1. Dessa forma, o D Flip-Flop serve como um elemento de armazenamento síncrono de 1 bit, sempre apresentando valores complementares nas saídas Q e Q'.

Os transistores Q1 e Q2 formam o latch propriamente dito, enquanto o transistor Q3 controla a passagem do dado de entrada e só permite sua condução quando há um pulso positivo em sua base. Esse pulso é gerado por um circuito diferenciador. Com isso o flip-flop torna-se sensível apenas à borda do sinal de clock, não respondendo ao nível estático, mas apenas às suas mudanças rápidas

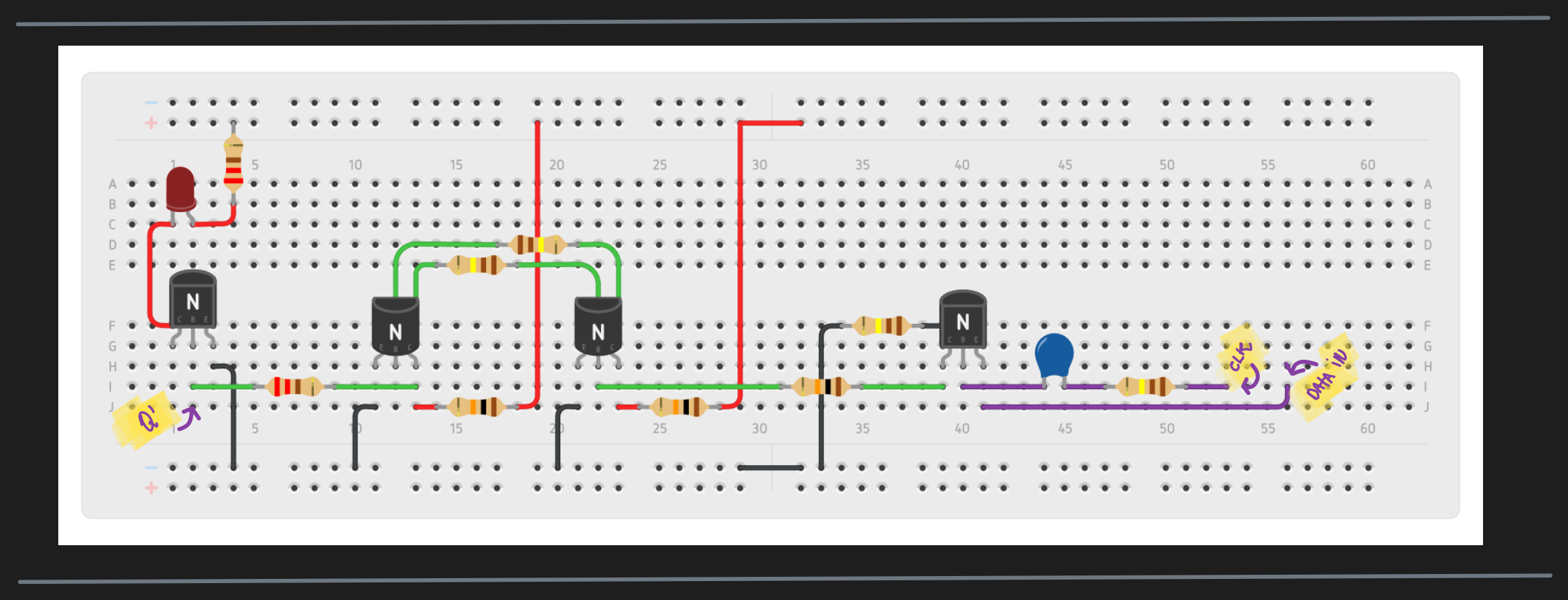

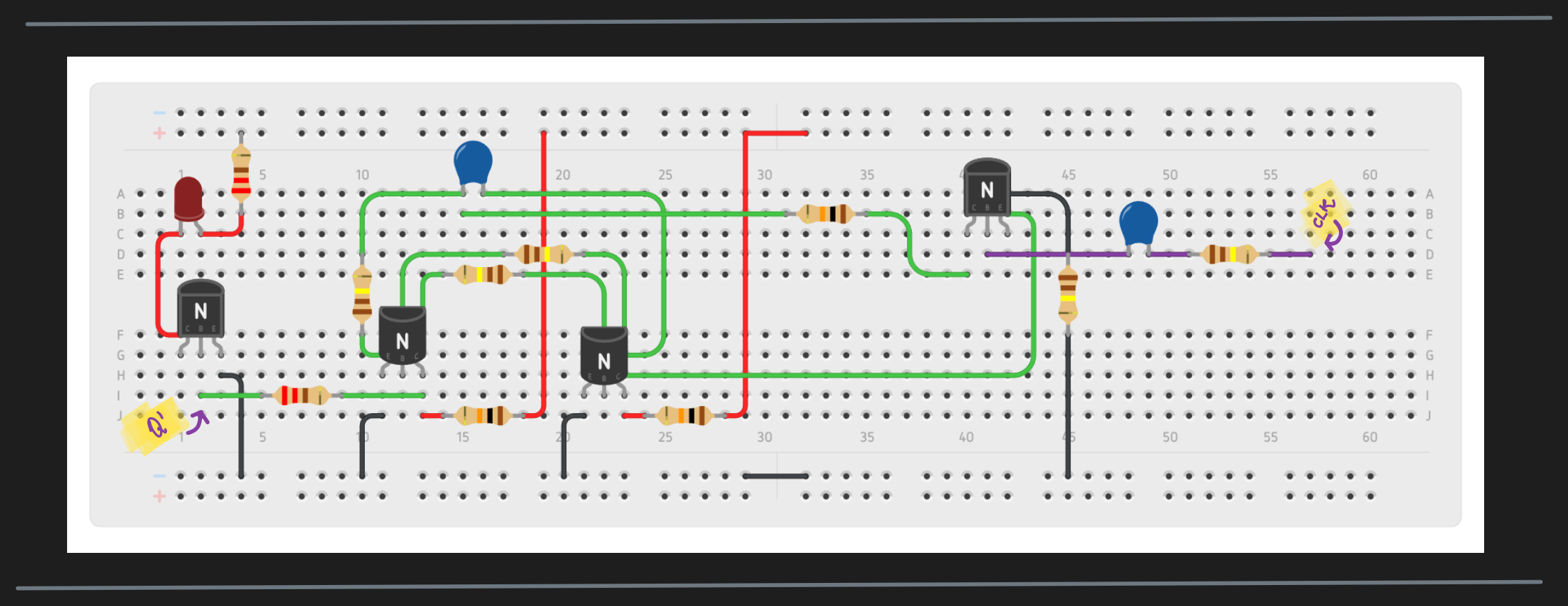

Protoboard

É importante entender que variar o nível em DATA IN não altera imediatamente as saídas Q ou Q'. A mudança real das saídas só ocorre no instante do pulso do clock. Até lá, DATA IN apenas define qual será o próximo valor capturado.

Na prática, se inicialmente a saída Q estiver em 1 e for aplicado um 0 em DATA IN, seguido por um pulso de clock, Q será alterada para 0. Se posteriormente DATA IN for colocado em 1 e ocorrer um novo pulso de clock, Q retornará ao valor 1. O flip-flop permanece insensível a variações fora desses momentos precisos.

Tabela Verdade

T Flip-Flop

O T Flip-Flop (Toggle Flip-Flop) é utilizado em contadores binários e circuitos sequenciais, tendo como principal característica a presença de uma única entrada (T). Diferentemente do D Flip-Flop, que armazena diretamente o valor presente em DATA IN, o T Flip-Flop altera seu estado conforme o sinal de controle aplicado à entrada T. Dessa forma, implementa uma função lógica de alternância comandada pelo clock.

A alteração de estado, assim como no D Flip-Flop, ocorre exclusivamente durante as transições do clock (bordas), garantindo operação síncrona e insensibilidade a mudanças fora desses instantes.

Esquemático

O T Flip-Flop pode ser implementado a partir de um D Flip-Flop, conectando a entrada D à saída complementar Q'. Com essa realimentação, o circuito garante que, a cada pulso de clock, o valor da saída seja invertido automaticamente, ou seja, se estava em 0, passa a 1, e vice-versa. Esse arranjo transforma o D Flip-Flop em um circuito de alternância automática.

Em circuitos discretos, para garantir que essa realimentação não cause um disparo imediato e incontrolado (loop direto), adiciona-se um capacitor em série na realimentação para criar um pequeno atraso entre saída e entrada. Esse atraso evita que a transição ocorra instantaneamente, impedindo a realimentação direta indesejada.

O resistor conectado ao capacitor é fundamental para descarregá-lo entre um pulso e outro. Sem esse resistor, o capacitor poderia permanecer carregado, impedindo o funcionamento correto do flip-flop, especialmente em sequências contínuas de clock.

Protoboard

Assim como no D Flip-Flop, a alternância de estado pode ser visualizada facilmente por meio de LEDs conectados às saídas. A cada pulso de clock, um LED conectado à saída acende enquanto o outro apaga, ilustrando de forma clara o funcionamento do circuito.

Tabela Verdade

Referências

- Código A Vida Secreta dos Computadores (Charles Petzold)

- Flip Flops Using Discrete Transistors